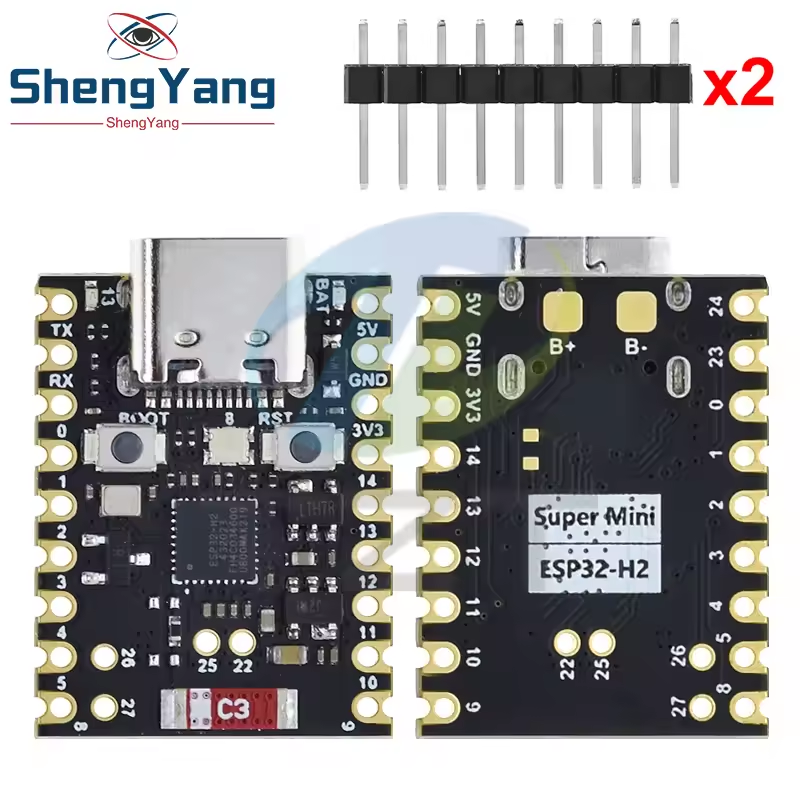

ESP32-H2 Super Mini is a development board based on the ESP32H2 microcontroller using RISCV32 architecture.

This board features a maximum CPU frequency of 96 MHz and 4MB flash memory.

About ESP32-H2 Super Mini

🆚 Wondering how the ESP32-S3 SuperMini compares to other SuperMini boards? Check out our full comparison guide to see how it stacks up against the C3, C3 Plus, C6, and H2.

Where to Buy ESP32-H2 Super Mini

Prices are subject to change. We earn from qualifying purchases as an Amazon Associate.

Technical Specifications

Complete technical specification details for ESP32-H2 Super Mini

Connectivity

Microcontroller

✨ Features & Pins

- • RISC-V 32-bit single-core CPU running at up to 96 MHz

- • 128 KB ROM, 320 KB SRAM, 4 KB Low-Power SRAM

- • 4 MB in-package flash memory

- • Supports IEEE 802.15.4 (Thread and Zigbee)

- • Bluetooth 5 Low Energy (BLE) support

- • Operates in the 2.4 GHz band with 250 Kbps data rate

- • USB Type-C interface for easy programming

- • Low-power consumption for battery-operated devices

Quick Setup

Copy-paste configs for ESP32-H2 Super Mini - auto‑generated from this board's exact hardware specs.

In Arduino IDE 2 select Esp32h2 Dev from the esp32 by Espressif package. In PlatformIO use board = esp32-h2-devkitm-1. ESP32H2 · 96 MHz · 4MB · QIO · RISC-V.

In Arduino IDE 2, open Boards Manager, search "esp32" by Espressif and install it. Then go to Tools → Board and select "Esp32h2 Dev" for the ESP32-H2 Super Mini.

[env:esp32-h2-super-mini]

platform = espressif32

board = esp32-h2-devkitm-1

framework = arduino

; Exact hardware config for ESP32-H2 Super Mini

board_build.mcu = esp32h2

board_build.f_cpu = 96000000L

board_build.flash_size = 4MB

board_build.flash_mode = qio

board_upload.flash_size = 4MBThe board value is a close generic match - check PlatformIO board registry for an exact fit.

esp32:

board: esp32-h2-devkitm-1

framework:

type: arduino # or "esp-idf"

# ESP32-H2 Super Mini - 96 MHz ESP32H2

# Flash: 4MB | USB: N/APaste into your device's .yaml. See ESPHome ESP32 docs for full options.

esptool.py \

--chip esp32h2 \

--baud 921600 \

write_flash \

--flash_mode qio \

--flash_size 4MB \

0x0 bootloader.bin \

0x8000 partitions.bin \

0xe000 boot_app0.bin \

0x10000 firmware.binInstall: pip install esptool - replace firmware.bin with your binary - bootloader at 0x0

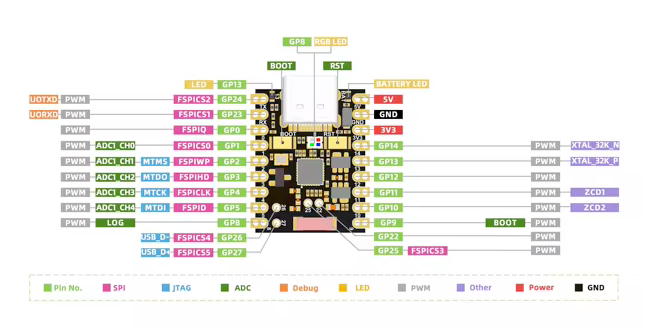

ESP32-H2 Super Mini Pinout Diagram

Complete pin reference for ESP32-H2 Super Mini

The ESP32-H2 Super Mini pinout is optimized for low-power and wireless communication applications. It includes essential power pins such as 5V, 3.3V, and GND for stable operation.

The board provides communication interfaces like RX and TX for UART, SDA and SCL for I2C, and MISO, MOSI, SCK, and SS for SPI, ensuring seamless integration with external devices.

For wireless connectivity, the ESP32-H2 SuperMini supports IEEE 802.15.4 for Thread/Zigbee and Bluetooth Low Energy (BLE), making it an excellent choice for mesh networking applications.

Safe Pins to Use

These pins are safe for general GPIO usage without boot or system conflicts

Why Are These Pins Safe?

Pins to Avoid or Use with Caution

Reserved for critical functions. Misuse may cause boot failures, programming issues, or system conflicts.

Boot behavior & flash voltage

Low-level debugging interface

USB Serial/JTAG communication

Memory & PSRAM connections

Debugging & firmware uploads

| PIN | Label | Why Avoid | Type |

|---|---|---|---|

| IO0 | GPIO0 | Connected to the external (or in-package) flash memory as a data line; cannot be repurposed without interfering with program storage. | ⚡ Flash |

| IO1 | GPIO1 | Used to select the SPI flash chip (not brought out on modules with in-package flash); needed for flash access, so it should not be used as a general IO. | ⚡ Flash |

| IO2 | MTMS | Serves as the flash memory’s write-protect pin and the JTAG TMS line; using it as GPIO can disrupt flash operation or JTAG debugging. | ⚡ Flash |

| IO3 | MTDO | Serves as the flash HOLD (D3) line and the JTAG TDO output; repurposing it can interfere with flash reads/writes or JTAG debugging. | ⚡ Flash |

| IO4 | MTCK | Acts as the SPI flash clock line and the JTAG clock; cannot be used as GPIO without halting flash operation or debug capability. | ⚡ Flash |

| IO5 | MTDI | Functions as the flash data input (D0) line and JTAG TDI input; using it as GPIO will interfere with the flash data bus and JTAG functionality. | ⚡ Flash |

| IO8 | GPIO8 | Must be held at the proper logic level on reset to select the correct boot mode and enable/disable bootloader log output. | 🛠️ Strapping |

| IO9 | GPIO9 | Must be pulled high on reset for normal SPI flash boot (pulling it low while GPIO8 is high forces the chip into download/programming mode). | 🛠️ Strapping |

| IO23 | U0RXD | Often used for the serial console and bootloader input; repurposing it may conflict with UART communication for programming or debugging. | 📡 UART |

| IO25 | GPIO25 | Used during boot to determine the JTAG interface source; this pin has no internal pull-up/down, so it must not be left floating (an external resistor drives it high/low to avoid unintended JTAG mode selection). | 🛠️ Strapping |

| IO26 | USB_D- | By default, this pin is connected to the chip’s internal USB Serial/JTAG peripheral; using it as a general-purpose IO requires disabling or reconfiguring that USB interface. | 🔌 USB |

| IO27 | USB_D+ | By default, this pin is connected to the internal USB Serial/JTAG controller; using it as a general-purpose IO would disable the USB functionality used for debugging/programming. | 🔌 USB |

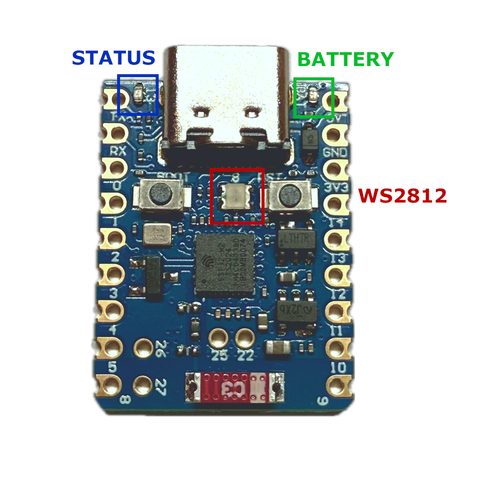

On-Board LEDs

LED indicators on ESP32-H2 Super Mini

The ESP32-H2 Supermini features three onboard LEDs: a green battery indicator, a user-controllable blue LED, and a WS2812 RGB LED. Note that the Blue LED and WS2812 share GPIO13 and GPIO8 respectively, and may interfere if both are driven simultaneously due to signal timing constraints.

🟢 Green LED – Battery Charge Indicator

- GPIO:

None - Control: Not controllable via GPIO

- Behavior:

- ⚡ Charging → LED on

- ✅ Battery connected → LED off

- 🔋 No battery → LED blinks

🔵 Blue LED – User Controllable

- GPIO:

GPIO13 - Control:

digitalWrite(), ESPHome GPIO output

void setup() {

pinMode(13, OUTPUT);

}

void loop() {

digitalWrite(13, HIGH);

delay(1000);

digitalWrite(13, LOW);

delay(1000);

}

output:

- platform: gpio

pin: 13

id: blue_led

light:

- platform: binary

name: "Blue LED"

output: blue_led

🌈 WS2812 LED – Programmable RGB

- GPIO:

GPIO8 - Control: FastLED, NeoPixel, etc.

#include <FastLED.h>

#define NUM_LEDS 1

#define DATA_PIN 8

CRGB leds[NUM_LEDS];

void setup() {

FastLED.addLeds<NEOPIXEL, DATA_PIN>(leds, NUM_LEDS);

}

void loop() {

leds[0] = CRGB::Red; FastLED.show(); delay(1000);

leds[0] = CRGB::Green; FastLED.show(); delay(1000);

leds[0] = CRGB::Blue; FastLED.show(); delay(1000);

light:

- platform: neopixelbus

type: GRB

pin: 8

num_leds: 1

name: "Onboard RGB LED"Useful Links

Datasheets and resources for ESP32-H2 Super Mini

ESP32-H2 Super Mini Custom Pin Mapping

Pin configuration and GPIO mapping for ESP32-H2 Super Mini

| Pin | Function | ESP Pin | I/O Type | Description |

|---|---|---|---|---|

| 1 | 5V | 5V | power input | 5V power input for the board |

| 2 | GND | GND | power ground | Ground connection |

| 3 | 3V3 | 3.3V | power output | 3.3V power output for peripherals |

| 4 | IO0 | GP0 | bidirectional | GPIO |

| 5 | IO1 | GP1 | bidirectional | GPIO, ADC pin |

| 6 | IO2 | GP2 | bidirectional | GPIO, ADC pin |

| 7 | IO3 | GP3 | bidirectional | GPIO, ADC pin |

| 8 | IO4 | GP4 | bidirectional | GPIO, ADC pin |

| 9 | IO5 | GP5 | bidirectional | GPIO, ADC pin |

| 12 | IO8 | GP8 | bidirectional | GPIO, LOG |

| 13 | IO9 | GP9 | bidirectional | GPIO, BOOT |

| 14 | IO10 | GP10 | bidirectional | GPIO |

| 15 | IO11 | GP11 | bidirectional | GPIO |

| 16 | IO12 | GP12 | bidirectional | GPIO |

| 17 | IO13 | GP13 | bidirectional | GPIO, LED |

| 18 | IO14 | GP14 | bidirectional | GPIO |

| 19 | IO22 | GP2 | bidirectional | GPIO |

| 20 | IO23 | GP23 | bidirectional | GPIO |

| 22 | IO25 | GP25 | bidirectional | GPIO |

| 23 | IO26 | GP26 | bidirectional | GPIO |

| 24 | IO27 | GP27 | bidirectional | GPIO |

Pin Mappings

Complete pinout and GPIO mapping for ESP32-H2 Super Mini

| Pin | Analog | Touch | PWM | Other |

|---|---|---|---|---|

| 0 | A0 | |||

| 1 | A1 | |||

| 2 | A2 | |||

| 3 | A3 | |||

| 4 | A4 | SCK | ||

| 5 | A5 | MISO | ||

| 6 | MOSI | |||

| 7 | SS | |||

| 8 | SDA | |||

| 9 | SCL | |||

| 20 | RX | |||

| 21 | TX |

Default Tools & Configuration

Build and upload settings for ESP32-H2 Super Mini

| Setting | Value |

|---|---|

| Bootloader tool | esptool_py |

| Uploader tool | esptool_py |

| Network uploader tool | esp_ota |

| Bootloader address | 0x0 |

| Flash mode | qio |

| Boot mode | qio |

| Maximum upload size | 1024 KB (1048576 bytes) |

| Maximum data size | 256 KB (262144 bytes) |

The ESP32-H2 Super Mini uses esptool_py for uploads , esp_ota for OTA updates, and esptool_py bootloader at 0x0.

Flash mode: qio | Boot mode: qio

Max sketch size: 1024 KB | Max data size: 256 KB

Similar Boards

Other development boards with ESP32H2 microcontroller

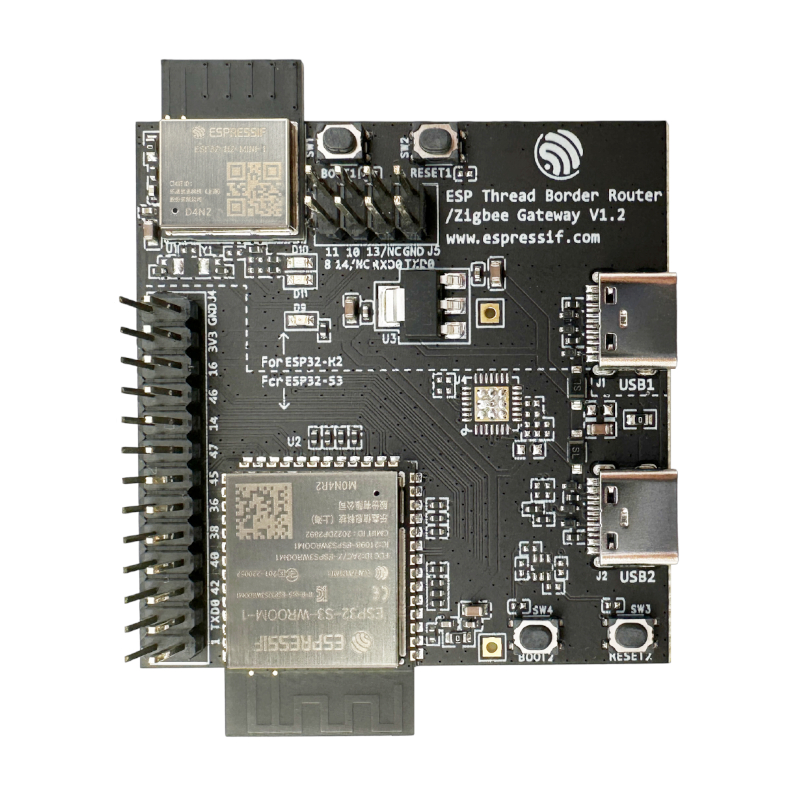

Espressif ESP Thread Border Router/Zigbee Gateway

Espressif ESP Thread Border Router/Zigbee Gateway development board is based on esp32h2 microcontroller and...

Espressif ESP32-H2-DevKitM-1

Espressif ESP32-H2-DevKitM-1 development board is based on esp32h2 microcontroller and uses riscv...