ESP32-S3 Super Mini Development Board Pinout and Technical Specifications

Code name: ESP32S3_DEV

ESP32-S3 Super Mini development board is based on esp32s3 microcontroller and uses xtensa architecture. This development board has a maximum CPU frequency of 240 MHz and a flash size of 4MB.

🛒 Price

📝 ESP32-S3 Super Mini Description

🚀 The ESP32-S3 SuperMini is a compact and powerful IoT development board based on the Espressif ESP32-S3 WiFi/Bluetooth dual-mode chip. Featuring a dual-core Xtensa LX7 processor running up to 240 MHz, it delivers impressive performance for your embedded projects. ⚡

📡 For seamless wireless connectivity, it supports WiFi 802.11b/g/n and Bluetooth 5 (LE), making it ideal for IoT applications. Just like the ESP32-C3 SuperMini, this board includes a built-in PCB antenna, ensuring reliable signal strength without requiring an external antenna.

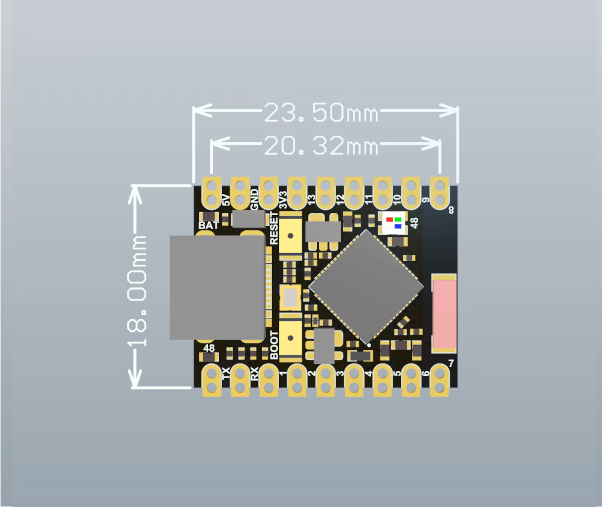

💾 Equipped with 512 KB SRAM and 4 MB flash memory, there's plenty of space for your firmware and applications. Its ultra-compact design (22.52 x 18 mm) makes it easy to embed into small projects

📟 ESP32-S3 Super Mini Case / Enclosure

Looking for a case to finish up your project with ESP32-S3 Super Mini? Check our 🛒 Etsy Store.

We offer a variety of enclosures for the ESP32 S3 Super Mini, available in different colors and configurations – with or without header pins, and more! You can also choose between a hexagon-patterned lid for improved heat dispersion ❄️ or a solid lid for a sleek finish.

On our 🛒 Etsy Store, you can find cases for different ESP32 development boards, the ESP32 boards with senors, screens, etc. The stock is always filling up! 📦

Need a custom case? ✉️ Contact Us on Etsy Store or our Contact Form

📊 ESP32-S3 Super Mini Specs

Below you can find the specifications of ESP32-S3 Super Mini, such as features, connectivity options, and ESP32-S3 Super Mini technical specs.

✨ Features

- Ultra-small size: 22.52 x 18 mm

- Ultra-low power consumption: deep sleep power consumption of about 43μA

- Onboard WS2812 RGB LED for programmable multi-color status indication

- Dual-core Xtensa LX7 CPU running at up to 240 MHz

- 512 KB SRAM, 384 KB ROM built-in, with 4 MB Flash

- Secure encryption features: AES-128/256, RSA, HMAC, digital signatures, and secure startup

- 11 digital IO pins

- 22 external interrupt pins

- 6 analog input pins

- 11 PWM pins

🛰️ Connectivity

- WiFi: 802.11 b/g/n (2.4 GHz)

- Bluetooth: 5.0

- BLE: 5.0

📐 Technical specs

| Microcontroller | esp32s3 |

| Clock Speed | 240 MHz |

| Flash size | 4MB |

| Architecture | xtensa |

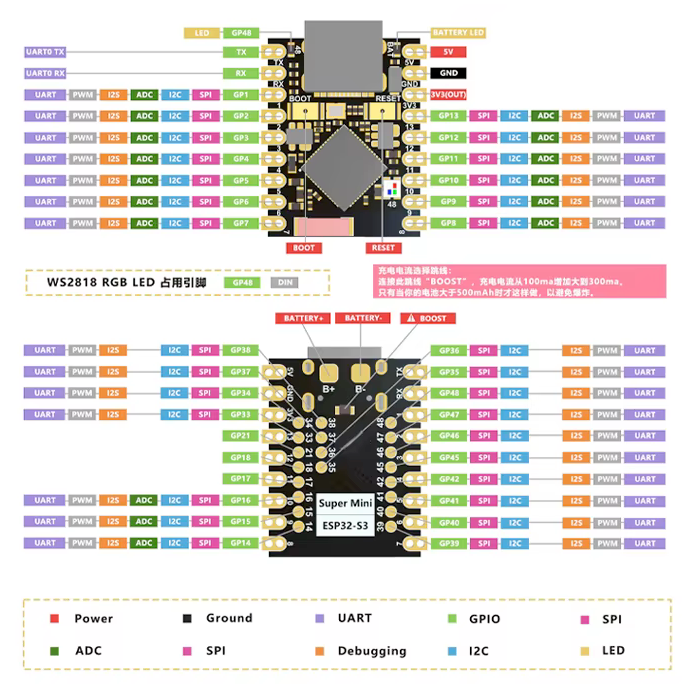

🔌 ESP32-S3 Super Mini Pinout

The ESP32-S3 Super Mini pinout is designed for maximum functionality in a compact package. The board provides essential power pins like 5V, 3.3V, and GND for stable power delivery.

It includes communication interfaces such as RX and TX for UART, SDA and SCL for I2C, and MISO, MOSI, SCK, and SS for SPI, ensuring seamless integration with peripherals.

For analog input, the ESP32-S3 Super Mini offers ADC pins labeled A0 to A5, making it suitable for sensor data acquisition. Additionally, it features an onboard WS2812 RGB LED, which allows programmable multi-color status indications for enhanced user feedback.

⚠️ Pins to Avoid or Use with Caution

Some pins are reserved for critical functions like bootstrapping, JTAG debugging, USB communication, and flash memory operations. Misusing these pins may lead to boot failures, programming issues, USB conflicts, or disruptions in flash storage. Below is a list of pins to avoid or use with caution, categorized for clarity:

- 🛠️ Strapping Pins (Boot Mode & System Behavior) - These pins control boot behavior and flash voltage selection. Pulling them high or low at reset can impact boot mode selection, voltage settings, or debugging access. Avoid altering their state unless necessary.

- 🔗 JTAG Debugging Pins - JTAG is used for low-level debugging and programming. If JTAG is enabled, these pins must remain dedicated to it. Repurposing them as GPIO can disable JTAG debugging features.

- 🔌 USB Communication Pins - These pins are used for USB Serial/JTAG communication. If USB debugging or communication is required, they should not be reassigned as GPIO.

- ⚡ Flash Memory & SPI Pins - Certain GPIOs are hardwired to SPI flash memory and PSRAM. Using them as standard GPIOs may result in system instability, corrupted storage, or boot failure.

- 📡 UART Serial Communication Pins - By default, these pins are used for serial debugging, console output, and firmware uploads. Repurposing them for general I/O may break UART programming or debugging capabilities.

| PIN | Label | Reason | Function |

|---|---|---|---|

| IO3 | GPIO3 | Sampled at reset to select JTAG interface (USB Serial/JTAG controller vs. external pins). Improper use can disable external JTAG or alter debug interface. | 🛠️ Strapping |

| IO9 | FSPIHD | Connected to external flash (data/hold signal) on most modules. Not recommended for use as GPIO, since it must remain dedicated to flash communication. | ⚡ Flash |

| IO10 | FSPICS0 | Used to select the external flash chip. It is required for flash access and cannot be repurposed without losing flash connectivity | ⚡ Flash |

| IO11 | FSPID | Used as a data line for flash (and in-package PSRAM). It should not be used as GPIO when the flash/PSRAM is in use. | ⚡ Flash |

| IO12 | FSPICLK | Drives the flash (and PSRAM) clock. This critical signal must be reserved for memory and not used as general GPIO. | ⚡ Flash |

| IO13 | FSPIQ | Used as a data line for flash/PSRAM transfers. Not available for other uses when flash/PSRAM is connected. | ⚡ Flash |

| IO14 | FSPIWP | Connected to external flash (data/write-protect signal). Not recommended as GPIO because it’s reserved for flash operations. | ⚡ Flash |

| IO33 | FSPIHD | On chips/modules with integrated flash, this IO is wired to the flash hold pin internally. It cannot be reassigned to GPIO without breaking flash access. | ⚡ Flash |

| IO34 | FSPICS0 | Wired to the chip select of the internal flash in flash-equipped variants. It must remain low during flash operation, so it’s not available for other use. | ⚡ Flash |

| IO35 | FSPID / PSRAM_D0 | In modules with octal PSRAM, this pin is connected to the PSRAM data line. It is reserved for memory interface and not free for general GPIO when flash/PSRAM is present. | ⚡ Flash |

| IO36 | FSPICLK / PSRAM_CLK | In modules with octal PSRAM, this pin drives the PSRAM clock. It must be dedicated to the memory interface, not used as a regular GPIO when that interface is in use. | ⚡ Flash |

| IO37 | FSPIQ / PSRAM_DQS | In modules with octal PSRAM, this pin is connected to the PSRAM’s DQS signal. It cannot be repurposed without disrupting the PSRAM/flash communication. | ⚡ Flash |

| IO38 | FSPIWP | On flash-equipped chips, this pin is tied to the flash’s WP# (or D3) line. It should be avoided for other use, as it’s needed for flash operations. | ⚡ Flash |

| IO39 | MTCK (GPIO39) | Default JTAG debugging TCK pin. If JTAG is needed, this pin must be free; it may also be used internally for PSRAM chip select on certain modules, so avoid repurposing it. | 🪛 Other |

| IO40 | MTDO (GPIO40) | Default JTAG TDO output for debugging. Using it as GPIO will interfere with JTAG debugging functionality. | 🪛 Other |

| IO41 | MTDI (GPIO41) | Default JTAG TDI input for debugging. Should be reserved for JTAG or left unused if JTAG is to remain available. | 🪛 Other |

| IO45 | GPIO45 | Determines flash/PSRAM power voltage (3.3 V vs 1.8 V) at boot. Must match hardware configuration; using as GPIO can upset flash supply setting. | 🛠️ Strapping |

| IO46 | GPIO46 | Must be at a defined level during reset (with GPIO0) to select normal or download boot and UART/USB print mode. This pin is input-only (no output drive), so it should be left for its intended strapping function. | 🛠️ Strapping |

| IO47 | SPICLK_P | Used only on variants with Octal SPI interface (e.g. ESP32-S3R16V) as part of the differential clock pair. On such chips it operates at 1.8 V and is reserved for the high-speed octal SPI clock, not for general GPIO use. | ⚡ Flash |

| IO48 | SPICLK_N | Used only on variants with Octal SPI interface, as the negative leg of the differential clock&. On such chips it operates at 1.8 V; it should be avoided for GPIO to prevent conflicts with the octal flash/PSRAM clock. | ⚡ Flash |

📌 Key Takeaway:

- Before using any GPIO, check if it is assigned a critical function.

- Avoid using bootstrapping pins unless you're modifying boot behavior intentionally.

- If JTAG debugging is needed, ensure its pins remain free.

- USB and Flash-related GPIOs should remain dedicated unless you disable their default functions.

✅ Pins Safe to use

- 🔹 IO1

- 🔹 IO2

- 🔹 IO4

- 🔹 IO5

- 🔹 IO6

- 🔹 IO7

- 🔹 IO8

- 🔹 IO15

- 🔹 IO16

- 🔹 IO17

- 🔹 IO18

- 🔹 IO21

Unlike restricted pins, these GPIOs are not tied to essential system functions like 🛠️ bootstrapping, 🔌 USB communication, 🔗 JTAG debugging, or ⚡ SPI flash memory, making them the best choices for custom applications and general use.

Why Are These Pins Safe?- Not involved in bootstrapping → These GPIOs do not affect the device’s boot mode or system startup.

- Not linked to flash memory or PSRAM → They won’t interfere with storage or memory access.

- Not dedicated to USB or JTAG → They remain free for general use without affecting debugging or programming.

- No special hardware connections → Unlike some pins that are internally wired to system functions, these remain freely assignable.

🗺️ ESP32-S3 Super Mini External Pins Mapping Functions

Below you can find the ESP32-S3 Super Mini pinout. This development board provides 11 digital IO pins, out of which 22 can be used as an external interrupt pins , 6 as analog input pins and 11 pins have Pulse-Width Modulation (PWM) .

| Pin | Function | ESP Pin | Input/Output | Description |

|---|---|---|---|---|

| 1 | 5V | 5V | POWER INPUT | 5V power input for the board |

| 2 | GND | GND | POWER GROUND | Ground connection |

| 3 | 3V3 | 3.3V | POWER OUTPUT | 3.3V power output for peripherals |

| 4 | TX | TX | TX | TX |

| 5 | RX | RX | RX | RX |

| 6 | IO1 | GP1 | BIDIRECTIONAL | GPIO, ADC Pin |

| 7 | IO2 | GP2 | BIDIRECTIONAL | GPIO, ADC pin |

| 8 | IO3 | GP3 | BIDIRECTIONAL | GPIO, ADC pin |

| 9 | IO4 | GP4 | BIDIRECTIONAL | GPIO, ADC pin |

| 10 | IO5 | GP5 | BIDIRECTIONAL | GPIO, ADC pin |

| 11 | IO6 | GP6 | BIDIRECTIONAL | GPIO, ADC pin |

| 12 | IO7 | GP7 | BIDIRECTIONAL | GPIO, ADC pin |

| 13 | IO8 | GP8 | BIDIRECTIONAL | GPIO, ADC pin |

| 14 | IO9 | GP9 | BIDIRECTIONAL | GPIO, ADC pin |

| 15 | IO10 | GP10 | BIDIRECTIONAL | GPIO, ADC pin |

| 16 | IO11 | GP11 | BIDIRECTIONAL | GPIO, ADC pin |

| 17 | IO12 | GP12 | BIDIRECTIONAL | GPIO, ADC pin |

| 18 | IO13 | GP13 | BIDIRECTIONAL | GPIO, ADC pin |

| 19 | IO14 | GP14 | BIDIRECTIONAL | GPIO, ADC pin |

| 20 | IO15 | GP15 | BIDIRECTIONAL | GPIO, ADC pin |

| 21 | IO16 | GP16 | BIDIRECTIONAL | GPIO, ADC pin |

| 22 | IO17 | GP17 | BIDIRECTIONAL | GPIO |

| 23 | IO18 | GP18 | BIDIRECTIONAL | GPIO |

| 24 | IO21 | GP21 | BIDIRECTIONAL | GPIO |

| 25 | IO33 | GP33 | BIDIRECTIONAL | GPIO |

| 26 | IO34 | GP34 | BIDIRECTIONAL | GPIO |

| 27 | IO35 | GP35 | BIDIRECTIONAL | GPIO |

| 28 | IO36 | GP36 | BIDIRECTIONAL | GPIO |

| 29 | IO37 | GP37 | BIDIRECTIONAL | GPIO |

| 30 | IO38 | GP38 | BIDIRECTIONAL | GPIO |

| 31 | IO39 | GP39 | BIDIRECTIONAL | GPIO |

| 32 | IO40 | GP40 | BIDIRECTIONAL | GPIO |

| 33 | IO41 | GP41 | BIDIRECTIONAL | GPIO |

| 34 | IO45 | GP45 | BIDIRECTIONAL | GPIO |

| 35 | IO46 | GP46 | BIDIRECTIONAL | GPIO |

| 36 | IO47 | GP47 | BIDIRECTIONAL | GPIO |

| 37 | IO48 | GP48 | BIDIRECTIONAL | GPIO |

🗺️ ESP32-S3 Super Mini Pins Mapping Arduino IDE

Below you can find the ESP32-S3 Super Mini pinout. This development board provides 11 digital IO pins, out of which 22 can be used as an external interrupt pins , 6 as analog input pins and 11 pins have Pulse-Width Modulation (PWM) .

| Pin | Analog | Touch | PWM | Other |

|---|---|---|---|---|

| 0 | A0 | |||

| 1 | A1 | |||

| 2 | A2 | |||

| 3 | A3 | |||

| 4 | A4 | SCK | ||

| 5 | A5 | MISO | ||

| 6 | MOSI | |||

| 7 | SS | |||

| 8 | WS2812_RGB SDA | |||

| 9 | SCL | |||

| 20 | RX | |||

| 21 | TX |

🛠️ Default Tools

| Bootloader tool | esptool_py |

| Uploader tool | esptool_py |

| Network uploader tool | esp_ota |

| Bootloader address | 0x0 |

| Flash mode | qio |

| Boot mode | qio |

| PSRAM type | |

| Maximum upload size | 1280 Kb (1310720 B) |

| Maximum data size | 320 Kb (327680 B) |

The ESP32-S3 Super Mini development board by default uses esptool_py uploader tool, esp_ota network uploader tool for Over-the-air (OTA) uploads and esptool_py bootloader tool. The bootloader starts at address "0x0". Flash mode and boot mode for ESP32-S3 Super Mini development board by default is qio and qio respectively.